### **Table of Contents**

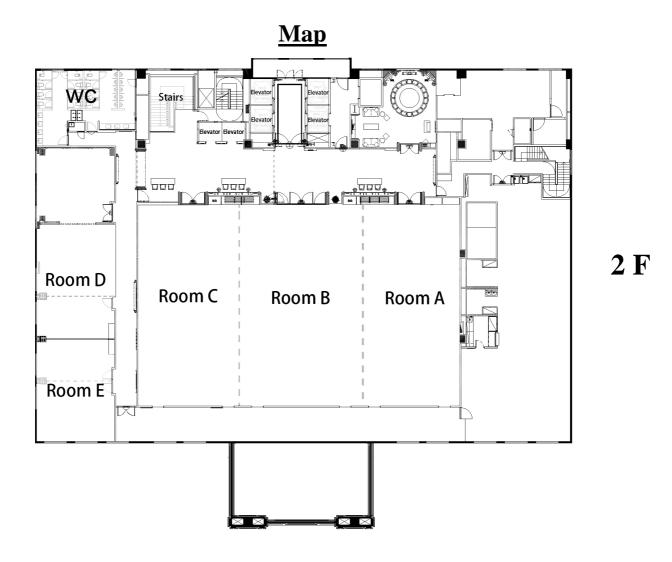

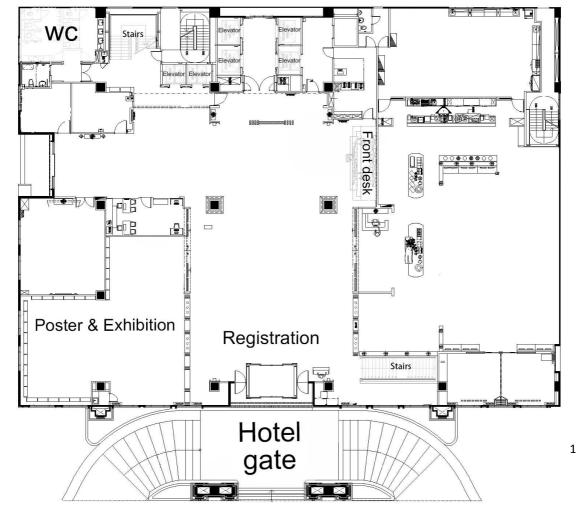

| Map                         | 1  |

|-----------------------------|----|

| Schedule                    | 2  |

| Organizers                  | 4  |

| Sponsors                    | 5  |

| General Information         | 6  |

| General Program Information | 8  |

| Speakers                    | 9  |

| Plenary Session             | 13 |

| Oral Session                | 20 |

| Poster Session              | 68 |

1 F

### **IEDMS 2014 Timetable**

|                |                           |                  |                                    |                                  | Nov. 20                              |           |                          |                                |          |                         |

|----------------|---------------------------|------------------|------------------------------------|----------------------------------|--------------------------------------|-----------|--------------------------|--------------------------------|----------|-------------------------|

| 08:00-17:00    | On-Site Registration      |                  |                                    |                                  |                                      |           |                          |                                |          |                         |

| 09:10-09:20    |                           | Opening Ceremony |                                    |                                  |                                      |           |                          |                                |          |                         |

| 09:20-10:00    |                           |                  | Plenary Session                    | 1 – Prof.                        | JG. Hwu (NTU                         | ) Chair:  | Prof. TY. Ts             | seng (NCTU)                    |          |                         |

| 10:00-10:30    |                           |                  |                                    |                                  | Coffee B                             | reak      |                          |                                |          |                         |

| 10:30-11:10    |                           |                  | Plenary Session                    | n 2 – Pro                        | f. J. J. Liou (UC)                   | F) Chair: | Prof. YC. H              | Io (NDHU)                      |          |                         |

| 11:10-11:50    |                           |                  | Plenary Session                    | on 3 – Di                        | : S. Yuasa (AIST                     | ) Chair:  | Prof. H. Ishiv           | vara (TIT)                     |          |                         |

| 12:00-13:30    |                           |                  |                                    |                                  | Lunch                                | 1         |                          |                                |          |                         |

|                |                           |                  |                                    | Invited                          | & Oral Sessions                      | 3         |                          |                                |          |                         |

|                | Session 1 (Roo<br>FinFET  | om A)            | Session 2 (Room B)<br>Solar Cell I |                                  | on 3 (Room C)<br>und Semiconductor I |           | 4 (Room D)<br>Simulation | Session 5 (I<br>Novel De       |          | Poster<br>Session 1     |

|                | Prof. S. S. Chu<br>(NCTU) | ung              | Prof. CF. Lin                      | Prof                             | H. Yamaguchi                         |           | . Z. Liu                 | Prof. M.<br>(HKUS              |          | (1F)                    |

| 13:30-15:00    | Chair: Prof. JG           | . Hwu            | (NTU)<br>Chair: Prof. WS. Liu      | Chair                            | : Prof. MC. Wu                       |           | ESTC)<br>of. CH. Lien    | Chair: Prof. H                 | C. Cheng | 13:00-15:00             |

|                | (NTU)<br>#1209            |                  | (YZU)<br>#1134                     |                                  | (NTHU)<br>#1178                      |           | ITHU)<br>1083            | (NCT)<br>#114                  |          | Chair:                  |

|                | #1212                     |                  | #1213                              |                                  | #1197                                |           | 1154                     | #127                           |          | Prof. MH. Lee<br>(NTNU) |

|                | #1308<br>#1332            |                  | #1310                              |                                  | #1243<br>#1345                       |           | 1343                     | #131<br>#134                   |          | (11110)                 |

| 15.00.15.20    | π1332                     |                  | #1363                              |                                  |                                      |           | 1350                     | #154                           | .2       |                         |

| 15:00-15:30    |                           |                  |                                    | т '.                             | Coffee Br                            |           |                          |                                |          |                         |

|                | G : (/P                   | • •              | G : 7(P P)                         |                                  | & Oral Sessions                      |           | 2 (D D)                  | G : 10 (F                      | , E)     |                         |

|                | Session 6 (Roo<br>TFT I   | om A)            | Session 7 (Room B)<br>LED          |                                  | on 8 (Room C)<br>vel Device II       |           | 9 (Room D)<br>ET I       | Session 10 (F<br>Nonvolatile M |          | Poster                  |

|                | Prof. M. War              | ng               | Prof. CM Tan                       | P                                | rof. R. Huang                        | Prof. S   | SI. Ohmi                 | Prof. KI                       | L. Pey   | Session 2               |

|                | (SU)                      |                  | (CGU)                              |                                  | (PKU)                                |           | TIT)                     | (SUTI<br>Chair: Prof.          | D)       | (1F)                    |

| 15:30-17:30    | Chair: Prof. S. S. (NCTU) | Chung            | Chair: Prof. CS. Lai<br>(CGU)      | Lai Chair: Prof. KN. Chen (NCTU) |                                      |           | f. MC. Wang<br>IUST)     | Chair: Prof.                   |          | 16:00-18:00             |

|                | #1129                     |                  | #1115                              |                                  | #1094                                |           | 1133                     | #111                           |          | Chair:                  |

|                | #1156                     |                  | #1257                              |                                  | #1106                                |           | 1144                     | #123<br>#123                   |          | Prof. CH. Liu           |

|                | #1185<br>#1289            |                  | #1261<br>#1283                     |                                  | #1111<br>#1322                       |           | 1192<br>1208             | #125                           |          | (NTNU)                  |

|                | #1209                     |                  | #1203                              |                                  | #1322                                |           | 1225                     | #129                           |          |                         |

|                |                           |                  |                                    |                                  |                                      |           | 1359                     | #130                           | 6        |                         |

| 17:30-18:30    |                           |                  |                                    |                                  | EDMA Annual                          | Meeting   |                          |                                |          |                         |

| 18:30-20:30    |                           |                  |                                    |                                  | Banque                               | et        |                          |                                |          |                         |

| Poste          | r Session 1 (             | (Nov.            | 20 13:00-15:00                     | )                                |                                      |           |                          |                                |          |                         |

| #1074          | #1075                     | #108             |                                    | #1086                            | #1087                                | #1089     | #1099                    | #1100                          | #1103    |                         |

| #1108          | #1120                     | #112             |                                    | #1135                            | #1137                                | #1150     | #1159                    | #1160                          | #1163    |                         |

| #1164          | #1166                     | #117             |                                    | #1186                            | #1187                                | #1193     | #1196                    | #1200                          | #120     |                         |

| #1215          | #1223                     | #122             |                                    | #1232                            | #1239                                | #1245     | #1246                    | #1247                          | #125     |                         |

| #1252          | #1265                     | #127             |                                    | #1280                            | #1284                                | #1290     | #1294                    | #1300                          | #130:    |                         |

| #1314<br>#1360 | #1324                     | #132             | 26 #1328                           | #1330                            | #1331                                | #1336     | #1338                    | #1349                          | #135     | 8                       |

|                | r Session 2.4             | (Nov             | 20 16:00-18:00                     | )                                |                                      |           |                          |                                |          |                         |

| #1079          | #1090                     | #109             |                                    | #1098                            | #1102                                | #1110     | #1117                    | #1118                          | #1128    | R                       |

| #1079          | #1090<br>#1140            | #109             |                                    | #1098                            | #1102                                | #1110     | #1117<br>#1216           | #1118<br>#1217                 | #1120    |                         |

| #1130          | #1140                     | #113             |                                    | #1182                            | #1136                                | #1214     | #1216                    | #1217                          | #1249    |                         |

| #1219          | #1220                     | #125             |                                    | #1229                            | #1230<br>#1267                       | #1258     | #1244                    | #1248                          | #124     |                         |

| #1235<br>#1285 | #1236<br>#1286            | #125             |                                    | #1302                            | #1207                                | #1312     | #1315                    | #1323                          | #132     |                         |

| #1283          | #1230                     | #134             |                                    | #1356                            | #1361                                | #1312     | #1315                    | #1366                          | #136     |                         |

| 1009           |                           | 10               | 1002                               |                                  | 1001                                 |           | 1505                     |                                | 150      | 2                       |

### **IEDMS 2014 Timetable**

|             |                                  |                                      | Nov. 21                                |                                 |                                              |                         |  |

|-------------|----------------------------------|--------------------------------------|----------------------------------------|---------------------------------|----------------------------------------------|-------------------------|--|

| 08:00-12:00 |                                  | On-Site Registration                 |                                        |                                 |                                              |                         |  |

|             | Oral Sessions                    |                                      |                                        |                                 |                                              |                         |  |

|             | Session 11 (Room A)              | Session 12 (Room B)                  | Session 13 (Room C)                    | Session 14 (Room D)             | Session 15 (Room E)                          |                         |  |

|             | Compound Semiconductor II        | Sensor                               | Novel Device III                       | Best Paper Competition I        | Best Paper Competition II                    |                         |  |

| 08:45-10:00 | Chair: Prof. WC. Hsu<br>(NCKU)   | Chair: Prof. JC. Wang<br>(CGU)       | Chair: Prof. TK. Chiang<br>(NUK)       | Chair: Prof. HC. Lin<br>(NCTU)  | Chair: Prof. PW. Li<br>(NCU)                 |                         |  |

|             | #1093                            | #1132                                | #1085                                  | #1109                           | #1077                                        |                         |  |

|             | #1113                            | #1157                                | #1143                                  | #1139                           | #1080                                        |                         |  |

|             | #1149                            | #1168                                | #1177                                  | #1191                           | #1107                                        | Poster                  |  |

|             | #1190                            | #1170                                | #1277                                  | #1254                           | #1141                                        | Session 3               |  |

|             | #1281                            | #1351                                | #1295                                  | #1325                           | #1204                                        | (1F)                    |  |

| 10:00-10:30 |                                  |                                      | Coffee Break                           |                                 |                                              | 09:00-11:00             |  |

|             | Invited & Oral Sessions          |                                      |                                        |                                 |                                              |                         |  |

|             | Session 16 (Room A)<br>TFT II    | Session 17 (Room B)<br>Solar Cell II | Session 18 (Room C)<br>Novel Device IV | Session 19 (Room D)<br>FET II   | Session 20 (Room E)<br>Nonvolatile Memory II | Prof. CH. Lin<br>(NDHU) |  |

| 10:30-12:00 | Prof. HC. Lin<br>(NCTU)          | Prof. TF. Guo<br>(NCKU)              | Prof. PW. Li<br>(NCU)                  | Prof. TK. Chiang<br>(NUK)       | Dr. C. Ho (Winbond)                          |                         |  |

| 10.30-12.00 | Chair: Prof. ST. Chang<br>(NCHU) | Chair: Prof. CC. Wu<br>(NTU)         | Chair: Prof. YL. Jiang<br>(NCHU)       | Chair: Prof. BY. Tsui<br>(NCTU) | Chair: Prof. TH. Hou<br>(NCTU)               |                         |  |

|             | #1084                            | #1195                                | #1124                                  | #1116                           | #1258                                        |                         |  |

|             | #1088                            | #1222                                | #1145                                  | #1165                           | #1276                                        |                         |  |

|             | #1167                            | #1292                                | #1153                                  | #1173                           | #1317                                        |                         |  |

|             | #1335                            | #1364                                | #1158                                  | #1313                           | #1319                                        |                         |  |

| 12:00-12:30 | Closing & Award                  |                                      |                                        |                                 |                                              |                         |  |

| 12:30-13:30 | Lunch                            |                                      |                                        |                                 |                                              |                         |  |

| 14:00-16:00 | MOST (NSC) Annual Meeting        |                                      |                                        |                                 |                                              |                         |  |

| Poster : | Session 3 | (Nov. 21 | 09:00-11:0 | <b>)</b> 0) |       |       |       |       |       |

|----------|-----------|----------|------------|-------------|-------|-------|-------|-------|-------|

| #1078    | #1082     | #1097    | #1101      | #1104       | #1105 | #1112 | #1123 | #1126 | #1130 |

| #1131    | #1138     | #1142    | #1146      | #1152       | #1162 | #1169 | #1171 | #1174 | #1179 |

| #1180    | #1181     | #1203    | #1206      | #1207       | #1210 | #1211 | #1228 | #1230 | #1233 |

| #1240    | #1241     | #1242    | #1262      | #1263       | #1264 | #1268 | #1271 | #1273 | #1287 |

| #1288    | #1291     | #1293    | #1298      | #1304       | #1307 | #1309 | #1311 | #1318 | #1321 |

| #1329    | #1334     | #1337    | #1340      | #1344       | #1346 | #1353 | #1355 |       |       |

### **Organizers**

##

### **Co-organizers**

### **Sponsors**

### NARLabs 國家實驗研究院

## 國家奈米元件實驗室

### **General Information**

#### **Organizer:**

Electronics Devices and Materials Association (EDMA)

Ministry of Science and Technology (MOST)

National Dong Hwa University (NDHU)

#### **Honorary Conference Chair:**

Maw-Kuen Wu, President, NDHU

#### **Conference Chair (List by Alphabet):**

Ro-Min Weng, NDHU (Chair)

Huang-Chung Cheng, EDMA (Co-Chair)

Tai-Ping Sun, EDMA (Co-Chair)

Tseung-Yuen Tseng, MOST (Co-Chair)

#### **International Advisory Committee (List by Alphabet):**

Hiroshi Ishiwara, Tokyo Institute of Technology, Japan

Juin J. Liou, University of Central, USA

Weiguang Zhu, Nanyang Technological University, Singapore

#### **Organizing Committee (List by Alphabet):**

Chun-Chieh Lin, NDHU (Chair)

Chia-Hua Huang, NDHU

Chu-Hsuan Lin, NDHU

Chuan-Hsi Liu, NTNU

Keng-Ming Liu, NDHU

Mei-Hsin Chen, NDHU

Ying-Chieh Ho, NDHU

Yu-Shyan Lin, NDHU

#### **Program Committee (List by Alphabet):**

Chu-Hsuan Lin, NDHU (Chair)

Bing-Yue Tsui, NCTU (Co-Chair)

Chung-Chih Wu, NTU (Co-Chair)

Horng-Chih Lin, NCTU (Co-Chair)

Wei-Chou Hsu, NCKU (Co-Chair)

Bae-Heng Tseng, NSYSU

Chao-Hsin Chien, NCTU

Chao-Sung Lai, CGU

Cheewee Liu, NTU

Chen-Hsin Lien, NTHU

Chia-Hua Huang, NDHU

Chuan-Hsi Liu, NTNU

Chun-Chieh Lin, NDHU

Chun-Yu Lin, NTNU

Edward Yi Chang, NCTU

Hao-Hsiung Lin, NTU

Jeng-Tzong Sheu, NCTU

Jenn-Gwo Hwu, NTU

Jer-Chyi Wang, CGU

Jr-Hau He, NTU

Keng-Ming Liu, NDHU

Kuan-Neng Chen, NCTU

Kuei-Shu Chang-Liao, NTHU

Li-Yin Chen, NSYSU

Mei-Hsin Chen, NDHU

Meng-Chyi Wu, NTHU

Pei-Wen Li, NCU

Shoou-Jinn Chang, NCKU

Shu-Tong Chang, NCHU

Tsong-Sheng Lay, NCHU

Tuo-Hung Hou, NCTU

Wen-Kuan Yeh, NDL

Yeong-Her Wang, NCKU

Yeu-Long Jiang, NCHU

Ying-Chieh Ho, NDHU

You-Lin Wu, NCNU

Yu-Shyan Lin, NDHU

Yue-Ming Hsin, NCU

#### **Secretariat:**

Min-Lin Chen, NDHU

S.-F. Lo, EMDA

### **General Program Information**

2014 International Electron Devices and Materials Symposium (IEDMS 2014) will be held on Nov. 20-21, 2014, at Fullon Hotel, Hualien, Taiwan. The IEDMS 2014 is intended to provide a common forum for researchers, scientists, engineers, and practitioners throughout the world to present their latest research findings, ideas, developments, and applications in the area of semiconductor materials and devices. Topics of interest will include, but are not limited to, the following:

A.Compound Semiconductor Materials, Electronic and Photonic Devices

**B.Sustainable Energy Devices and Materials**

C.Integrated Circuits and Packaging Technologies

D.Nano Devices and Materials, Memories, Displays, and Sensors

#### **Important Dates:**

Abstract Submission: Aug. 31, 2014

Notification of Acceptance: Oct. 01, 2014

Early-Bird Registration Deadline: Oct. 31, 2014

Special Issue Deadline: Nov. 19, 2014

#### **For Invited Talks**

• Time for the invited talk is 30 minutes, including last 3 minutes for discussion.

#### **For Oral Papers**

- Time allotted for your presentation is 15 minutes, including last 3 minutes for discussion.

- Please report to the Session Chair and upload your PowerPoint file to the Notebook computer in the session room at least 10 minutes before the session begins.

#### **For Poster Papers**

• The size of a poster board is 90 cm (width) x 180 cm (height). The recommended size of your poster is A0 (84.1 cm (width) x 118.9 cm (height)).

#### Free WiFi Access

WiFi: Fullon\_Hotels HL Password: 888888888

### **Speakers (List by Session Schedule)**

#### **Plenary Speakers**

Prof. Jenn-Gwo Hwu 胡振國教授

National Taiwan University, Taiwan

Title: Nanoscale Oxide Engineering on Si Substrate

Time: Nov. 20 09:20-10:00 (Room B)

Prof. Juin J. Liou

University of Central Florida, USA

Title: Prospect and Outlook of Electrostatic Discharge (ESD)

Protection in Emerging Technologies Time: Nov. 20 10:30-11:10 (Room B)

Dr. Shinji Yuasa

National Institute of Advanced Industrial Science and Technology

(AIST), Japan

Title: Perspectives on Spintronics and MRAM Technologies

Time: Nov. 20 11:10-11:50 (Room B)

#### **Invited Speakers**

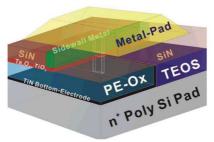

Prof. Steve S. Chung 莊紹勳教授

National Chiao Tung University, Taiwan

Title: The Experimental Observation of the Dopant Fluctuations

in Trigate FinFETs

Time: Nov. 20 13:30-14:00 (Room A)

Prof. Ching-Fuh Lin 林清富教授 National Taiwan University, Taiwan

Title: Semiconductor Nanostructures for Solar Cells

Time: Nov. 20 13:30-14:00 (Room B)

Prof. Hiroshi Yamaguchi

NTT Basic Research Laboratories, Japan

Title: Opto/electromechanical Resonators Based on

GaAs/AlGaAs Heterostructures

Time: Nov. 20 13:30-14:00 (Room C)

Prof. Zhiwei Liu

University of Electronic Science and Technology of China,

China

Title: High holding voltage SCR devices design for high

voltage ESD protection

Time: Nov. 20 13:30-14:00 (Room D)

Prof. Mansun Chan

Hong Kong University of Science & Technology, Hong Kong

Title: Developing a Post-Moore Collaborative Technology

Platform for Emerging Device Deployment

Time: Nov. 20 13:30-14:00 (Room E)

Prof. Mingxiang Wang

Soochow University, China

Title: Suppress Dynamic Hot Carrier Degradation in

Four-Terminal Poly-Si Thin Film Transistors

Time: Nov. 20 15:30-16:00 (Room A)

Prof. Cher-Ming Tan 陳始明教授

Chang Gung University, Taiwan

Title: Exploring the Humidity Effect on the Reliability of High

Power LEDs

Time: Nov. 20 15:30-16:00 (Room B)

Prof. Ru Huang

Peking University, China

Title: Junction Engineering of Tunnel FETs for Steep Switching

and Improved Noise Behavior

Time: Nov. 20 15:30-16:00 (Room C)

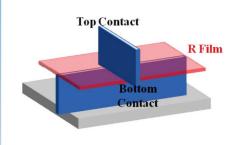

Prof. Shun-Ichiro Ohmi

Tokyo Institute of Technology, Japan

Title: Room Temperature Fabrication of Pentacene-Based OFETs with Hf-Based High-k Gate Insulator for Low Voltage

Operation

Time: Nov. 20 15:30-16:00 (Room D)

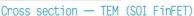

Prof. Kin-Leong Pey

Singapore University of Technology and Design, Singapore

Title: Filamentary Switching with Semiconducting Bottom

Electrode – Physical Insight and Advantages

Time: Nov. 20 15:30-16:00 (Room E)

Prof. Horng-Chih Lin 林鴻志教授

National Chiao Tung University, Taiwan

Title: Fabrication of Thin-Film Transistors/Inverters with Film

**Profile Engineering**

Time: Nov. 21 10:30-11:00 (Room A)

Prof. Tzung-Fang Guo 郭宗枋教授

National Cheng Kung University, Taiwan

Title: Nickel oxide p-type electrode interlayer in CH3NH3PbI3 perovskite/fullerene planar-heterojunction hybrid solar cells

Time: Nov. 21 10:30-11:00 (Room B)

Prof. Pei-Wen Li 李佩雯教授

National Central University, Taiwan

Title: Designer Germanium Quantum-Dot for Nanoeletronics

and Nanophotonics Devices

Time: Nov. 21 10:30-11:00 (Room C)

Prof. Te-Kung Chiang 江德光教授

National University of Kaohsiung, Taiwan

Title: A New Quasi-3D Compact Threshold Voltage Model for

Pi-Gate (PG) MOSFETs with the Interface Trapped Charges

Time: Nov. 21 10:30-11:00 (Room D)

Dr. ChiaHua Ho 何家驊博士

Winbond Electronics Corporation, Taiwan

Title: Overview of Emerging Non-Volatile Memories

Time: Nov. 21 10:30-11:00 (Room E)

### **Plenary Session 1**

Nov. 20, 09:20-10:00, 2F Room B

Prof. Jenn-Gwo Hwu

Distinguished Professor, National Taiwan University, Taiwan

**Presentation Title:** Nanoscale Oxide Engineering on Si Substrate

Authors: Po-Hao Tseng, Yen-Kai Lin, Han-Wei Lu, Yu-Ching Liao, and Jenn-Gwo

Hwu\*

#### Abstract:

Anodization technique was introduced for the oxide formation in nanoscale device application. There are two parts in this talk. Single crystal Si nanowires with dimension down to sub-10 nm can be formed by long time anodization. Several new phenomena were presented. Anodization with suitable condition can also form various oxide thicknesses on single wafer. It is useful to grow ultra-thin oxide with thickness smaller than 3 nm. The MOS structures with various oxide thicknesses will be characterized in the view point of I-V and C-V. There are several fundamental differences between MOS(p) and MOS(n) structures. The current in inversion becomes saturated when the oxide is thin enough. The saturation behavior is sensitive to temperature, illumination, and charge trapping. Therefore, valuable applications of nanoscale MOS devices are achievable. The physics left behind is of importance for nanoscale study.

#### **Biography**

Jenn-Gwo Hwu was born in Tainan, Taiwan, Republic of china, on August 29, 1955. He received the B.S. degree in electronic engineering from National Chiao-Tung University, Republic of China, in 1977 and the M.S. and Ph.D. degrees in electrical engineering from National Taiwan University, Republic of China, in 1979

and 1985, respectively.

He joined the faculty of National Taiwan University in 1981. Presently, he is a Professor in the Department of Electrical Engineering and the Graduate Institute of Electronics Engineering, National Taiwan University. From 1997 to 1998, he was the vice chairman of the Department of Electrical Engineering, National Taiwan University. From February 2004 to January 2006, he was invited as the Dean of the College of Electrical Engineering and Computer Science, National United University, Miaoli, Taiwan, Republic of China. From December 2005 to December 2008, he was invited as the Coordinator of Micro-Electronics Engineering Program, Department of Engineering and Applied Sciences, National Science Council, Taiwan, Republic of China. On August 2006, he was appointed as the Distinguished Professor of National Taiwan University. And from August 2007 to July 2010, he was appointed as the chairperson of the Department of Electrical Engineering, National Taiwan University. His research work is mainly on ultra-thin gate oxide and its related Si MOS devices. He has experience in teaching the courses of Circuits, Electronics, Solid-State Electronics, Semiconductor Engineering, MOS Capacitor Devices, Radiation Effects on MOS System, and Special Topic on Oxide Reliability.

He was qualified to be a licensed Professional and Technical Engineer on Electrical and Electronics Engineering, R.O.C., in 1978 and 1980, respectively. He was honored as the owner of Outstanding Teaching Award in 1991 by The Ministry of Education and in 1987, 2003, and 2008 by National Taiwan University. He was also the owner of Excellent Teaching Award in 1988, 1989, 1990, 1991, and 1993 by the College of Engineering, National Taiwan University, and in 1999, 2000, and 2002 by National Taiwan University. In 1999, he was the recipient of Jan Ten-You Paper Award by The Chinese Institute of Engineering, R.O.C. In 2005, he was the recipient of Scientific Paper Award by Far Eastern Y.Z.Hsu Science and Technology Memory Foundation, Taiwan, R.O.C. In 2012, he was awarded the Himax Chair Professorship at National Taiwan University.

#### **Major Research Areas**

Si MOS Devices/Ultra-thin Gate Oxide Processes/Novel Si-based Devices/Rapid Thermal Processing-RTP /Uniformity Analysis and Stress Control/Si MOS Solar Cell and Photo Sensors

### **Plenary Session 2**

Nov. 20, 10:30-11:10, 2F Room B

Prof. Juin J. Liou

Lockheed Martin St. Laurent Professor of Engineering, School of EECS, University of Central Florida

Presentation Title: Prospect and Outlook of Electrostatic Discharge (ESD)

Protection in Emerging Technologies

Author: Juin J. Liou

#### **Abstract:**

Electrostatic discharge (ESD) is a process in which a finite amount of charge is transferred from one object (i.e., human body) to the other (i.e., microchip). This process can result in a very high current passing through the object within a very short period of time [1-2]. When a microchip or electronic system is subject to an ESD event, the huge ESD-induced current can likely damage the microchip and cause malfunction to the electronic system if the heat generated in the object cannot be dissipated quickly enough. It is estimated that about 35% of all damaged microchips are ESD related, resulting in a revenue loss of several hundred million dollars in the global semiconductor industry every year [3]. The continuing diminishing in the size of MOS devices makes the ESD-induced failures even more prominent, and one can predict with certainty that the availability of effective and robust ESD protection solutions will become a critical component to the successful development of the CMOS-based integrated circuits.

Advancement of low-voltage electronics has been benefitted largely by the continue scaling of CMOS technology, which is now reaching an astonishing milestone of 22-nm node. Beyond that, several new features will need to be implemented to enable the continuation of CMOS miniaturization, including the high-k dielectric, metal gate, multiple gate, etc. A noteworthy future CMOS development is the Si nanowire

technology. It has the advantages of a superior gate control, excellent on-current vs. off-current ratio, very low power consumption, and extremely high cutoff frequency. The ESD protection issues of such a technology are still largely unknown at this time and need to be resolved urgently before the technology can be commercialized in the consumer market in about 3-4 years [4]. On the other hand, high-voltage electronics, such as those used in the automobiles, are increasingly important and popular. These SoC's are typically fabricated in the bipolar/CMOS/DMOS (BCD) process, and such applications imposed additional challenges on the design and implementation of high-voltage ESD protection solutions [5].

Some comments on the ESD standards are in order. Human body model is a mature, well-understood ESD model for simulating charge transfer from a person's finger to an electronic component. However, recent industry data indicates that the HBM rarely simulates real-world ESD failures. Latest generation package styles such as mBGAs, SOTs, SC70s, & CSPs with mm-range dimensions are often effectively too small for people to handle with fingers. Even in cases of relatively large components, most high-volume component and board manufacturing uses automated equipment, so humans rarely touch the components. Charged device model can more successfully replicate in-house and customer IC failures at the component level [6].

In the presentation, the fundamentals of ESD, including its mechanisms, standards, protection principles, and testing will first be introduced. This is followed by the exploration and evaluation of ESD protection solutions in emerging Si nanowire, organic, and GaN technologies.

Acknowledgements—This work was supported financially or in-kind by Analog Devices Inc., USA, Intersil Corp., USA, National Semiconductor Corp., USA, National Center for Nanomaterials Technology, Korea, Institute of Microelectronics, Singapore, and Ministry of Education, China.

#### **REFERENCES**

- [1] J. Vinson, G. Croft, J. Bernier, and J. J. Liou, Electrostatic Discharge Analysis and Design Handbook, Kluwer Academic Publishers, Boston, 2002.

- [2] J. Vinson and J. J. Liou, "Electrostatic discharge in semiconductor devices: protection techniques," (Invited Paper) Proceedings of the IEEE, vol. 88, pp. 1878-1900, Dec. 2000.

- [3] M. Brandt and S. Halperin, "What does ESD really cost?", Circuits Assembly

Magazine, June 1, 2003.

- [4] W. Liu, J. J. Liou, et al., "Electrostatic discharge (ESD) robustness of Si nanowire field-effect transistors," IEEE Electron Device Letters, vol. 30, pp. 969-971, Sept. 2009.

- [5] Z. Liu, J. J. Liou, and J. Vinson, "Novel silicon controlled rectifier for high-voltage ESD applications," IEEE Electron Device Letters, vol. 29, pp. 753-755, July 2008.

- [6] Z. Gan, W. Wong, and J. J. Liou, Semiconductor Process Reliability: in Practice, McGraw-Hill, New York, 2012.

#### **Honor and Awards**

Dr. Liou has been awarded 8 U.S. patents, and has published 10 books, 2 book chapter, more than 260 journal papers (including 16 invited articles), and more than 220 papers (including more than 90 keynote/invited papers) in international and national conference proceedings. He has been awarded over \$12.0 million of research contracts and grants from federal agencies, state government, and industry, and has held consulting positions with research laboratories and companies in the United States, China, Japan, Taiwan, and Singapore.

Dr. Liou was awarded the UCF Pegasus Distinguished Professor in 2009 – the highest honor bestowed to a faculty member at UCF, UCF Distinguished Researcher Award in 1992, 1998, 2002, and 2009, and IEEE Joseph M. Biedenbach Outstanding Engineering Educator Award in 2004. His other honors are Fellow of IEEE, Fellow of IET, and Chang Jiang Endowed Professor of Ministry of Education, China – the highest honorary professorship in China.

Dr. Liou has served as the IEEE EDS Vice-President of Regions/Chapters, IEEE EDS Treasurer, IEEE EDS Finance Committee Chair, Member of IEEE EDS Board of Governors, and Member of IEEE EDS Educational Activities Committee.

### **Plenary Session 3**

Nov. 20, 11:10-11:50, 2F Room B

Dr. Shinji Yuasa

Director, Spintronics Research Center, National Institute of Advanced Industrial Science and Technology (AIST), Japan

**Presentation Title:** Perspectives on Spintronics and MRAM Technologies

**Authors:** Shinji Yuasa, Kay Yakushiji, Akio Fukushima, Takayuki Nozaki, Yoichi Shiota, Makoto Konoto, Rie Matsumoto, Hitoshi Kubota, Koji Ando, and Y. Suzuki

#### **Abstract:**

This paper presents a review and perspectives on the tunnel magnetoresistance (TMR) effect in magnetic tunnel junction (MTJ) and spin manipulation technologies such as spin-transfer torque (STT) and voltage-induced torque for magnetoresistive random access memory (MRAM) and other novel devices. Major challenges for ultrahigh-density MRAM with perpendicular magnetization and novel functional devices are discussed.

#### **Education and Professional Experience**

Shinji Yuasa was born in Kanagawa Prefecture (Japan) in 1968. He received B.S. in Physics from Keio University (Yokohama, Japan) in 1991. He received PhD in Physics from Keio University in 1996. After receiving his doctorate, he served as a staff scientist at the Electrotechnical Laboratory (Tsukuba, Japan) where he worked on spin-dependent transport in metallic magnetic multilayers. Since 2001, he has been a staff scientist at the National Institute of Advanced Industrial Science and Technology (AIST), working on the physics and device applications of MTJs. Since 2010, he has been a director of the Spintronics Research Center at AIST. Since 2010, he has been concurrently holding a position of Professor at University of Tsukuba (Tsukuba, Japan). He has published more than 100 peer reviewed papers and has given more than 100 invited talks at international conferences. For his achievement of the giant TMR effect in MgO-based MTJs, he has been awarded or co-awarded 21 prizes, including the Asahi Award in 2007.

#### **Research Field**

His research field includes magnetism, magnetic materials, thin films and multilayers, and spintronics. For the last decade, he has been mainly working on tunnel magnetoresistance and spin-transfer torque in magnetic tunnel junctions (MTJs), especially MgO-based MTJs. He is interested in both the basic physics and device applications of MTJs.

#### **Contribution to Society**

Shinji Yuasa served as an Editor of Magnetics Society of Japan from 2001 to 2010. He also served as a member of Program Committees for 19th International Colloquium on Magnetic Films and Surfaces (ICMFS 2006), 55th Annual Conference on Magnetism and Magnetic Materials (MMM 2010), and IEEE International Magnetics Conference (Intermag 2011). He was a Vice-chair of Gordon Research Conference on Magnetic Nanostructure 2010 and a member of International Advisory Committee for The IEEE 7th International Symposium on Metallic Multilayers (MML 2010). He is now serving as a Program Co-chair for the 2013 Joint MMM/Intermag Conference, a member of the Advisory Committee for the MMM Conference, and a member of Program Committee for 21st International Colloquium on Magnetic Films and Surfaces (ICMFS 2012). He is an Editor of Applied Physics Express / Jpn. J. Appl. Phys. since 2009. He has also been assigned as the IEEE Distinguished Lecturer for 2012.

#### Recognition

He has been awarded or co-awarded the following scientific prizes:

- -IEEE Distinguished Lecturer for 2012

- -Japan Society for the Promotion of Science (JSPS) Prize (2010)

- -Tsukuba Prize (2010)

- -Inoue Harushige Prize (2009) (together with Canon-Anelva Corp.)

- -The Prime Minister Award of Japan (2008) (together with D. D. Djayaprawira and Y. Suzuki)

- -Asahi Award (2007) (together with T. Miyazaki)

- -IBM Japan Prize (2007)

- -Tokyo Techno Forum 21 Gold Medal (2006)

- -Marubun Science Prize (2006)

- -The Japan Society of Applied Physics (JSAP) Best Paper Award (2005)

- -Ichimura Science Prize (2004)

- -10 other prizes.

### **Oral Session**

#### Session 1: FinFET (November 20)

#### Room A

Chair: Prof. Jenn-Gwo Hwu, Department of Electrical Engineering, National Taiwan University, Taiwan

#### 13:30~14:00

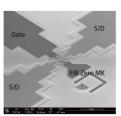

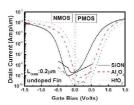

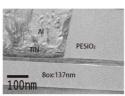

## (Invited) The Experimental Observation of the Dopant Fluctuations in Trigate FinFETs

Steve S Chung

The random dopant fluctuation is one of the most important issues for the 16nm and beyond CMOS technologies with trigate FinFET

Department of Electronics Engineering, National Chiao Tung University, Taiwan

structure in terms of the device architecture and manufacturing. This paper will demonstrate the methodology to understand the dopant fluctuation via a purely experimental approach. It will be demonstrated in advanced trigate FinFET devices. The discrete dopant distribution along the channel direction can be determined. Boron clustering effect in nMOSFETs can be reasonably explained which results in a larger Vth variation, in comparison to that of pMOSFETs. Moreover, experiments have been extended to the advanced trigate CMOS devices. The sidewall roughness and the LER(Line edge roughness) in trigate have also been examined. This approach provides a good monitor of the quality of 3D gate structure and the random dopant fluctuation (RDF) of advanced trigate

#### 14:00~14:15

## **#1209 Simulation Study of Gate and Fin Line Edge Roughness Effects on 14 nm Inversion-Mode and Junctionless FinFETs**

Li-Syun Yang, and Keng-Ming Liu

devices.

Department of Electronical Engineering, National Dong Hwa University, Taiwan

In this paper we simulated the gate and fin line edge roughness (LER) effects on the 14 nm inversion-mode (IM) and junctionless (JL) FinFETs. Different rms amplitudes of gate and fin LER were simulated to examine their effects on the device characteristics. The simulation results show that the gate LER effects are more significant than the fin LER effects except the on-state current. We also found that, as far as LER is concerned, JL FinFETs are more

|             | vulnerable than the IM FinEETs except that the on state assument                                        |

|-------------|---------------------------------------------------------------------------------------------------------|

|             | vulnerable than the IM FinFETs except that the on-state current                                         |

| 14.15.14.20 | fluctuation of the IM FinFETs is larger than that of the JL FinFETs.                                    |

| 14:15~14:30 | #1212 Vertically Stacked Nanowire Transistors Using                                                     |

|             | Low-Temperature Microwave Annealing                                                                     |

|             | Ming-Kun Huang <sup>1</sup> , Wen-Fa Wu <sup>2</sup> , and Chun-Hsing Shih <sup>1</sup>                 |

|             | <sup>1</sup> Department of Electrical Engineering, National Chi Nan University, Taiwan                  |

|             | <sup>2</sup> National Nano Device Laboratories, Taiwan                                                  |

|             | Thermal budget is one of the major concerns to fabricate                                                |

|             | three-dimensional nanowire transistors. This work uses                                                  |

|             | low-temperature microwave annealing to fabricate vertically stacked                                     |

|             | gate-all-around nanowire transistors. A microwave power of 400%                                         |

|             | and a processing time of 150s were used in post-implantation                                            |

|             | annealing to minimize thermal energy while retaining sufficient                                         |

|             | activation. The vertically stacked nanowire devices show nearly                                         |

|             | doubled drain currents compared to their non-stacked counterparts.                                      |

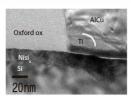

| 14:30~14:45 | $\#1308$ Fabrication and Characterization of $Al_2O_3/InAs$ Fin                                         |

|             | Field-Effect Transistors                                                                                |

|             | Cheng-Hsuan Hsieh <sup>1</sup> , Wei-Jen Hsueh <sup>1</sup> and Jen-Inn Chyi <sup>1,2,3,4,*</sup>       |

|             | <sup>1</sup> Department of Electrical Engineering, National Central University, Taiwan                  |

|             | <sup>2</sup> Optical Sciences Center, National Central University, Taiwan <sup>3</sup> National Applied |

|             | Research Laboratories, Taiwan <sup>4</sup> Research Center for Applied Science, Academia                |

|             | Sinica, Taiwan                                                                                          |

|             | Al <sub>2</sub> O <sub>3</sub> /n-InAs Fin Field-Effect Transistors (FinFETs) with gate                 |

|             | length of 0.5 μm, source to drain separation of 2 μm and effective                                      |

|             | fin width of 60 nm are demonstrated in this work. The FinFETs                                           |

|             | exhibit a maximum drain current density ( $I_{Dmax}$ ) of 119 $\mu A/\mu m$ , a                         |

|             | maximum transconductance ( $G_{mmax}$ ) of 77.2 $\mu S/\mu m$ , a threshold                             |

|             | voltage of -2.37 V, a drain current on-off ratio of 136, and a                                          |

|             | subthreshold swing of 524 mV/decade.                                                                    |

| 14:45~15:00 | #1332 Effect of Channel-Fin Width and Angle on Optimal                                                  |

|             | Characteristic of Trapezoidal-Shaped Bulk FinFET Devices                                                |

|             | Li-Wen Chen <sup>1,2</sup> and Yiming Li <sup>1,2,3,*</sup>                                             |

|             | <sup>1</sup> Parallel and Scientific Computing Laboratory, National Chiao Tung University,              |

|             | Taiwan <sup>2</sup> Institute of Communications Engineering, National Chiao Tung                        |

|             | University, Taiwan <sup>3</sup> Department of Electrical and Computer Engineering, National             |

|             | Chiao Tung University, Taiwan                                                                           |

|             | In this work, we study the 16-nm-gate trapezoidal HKMG bulk                                             |

|             | FinFET devices and its implication on static random access memory                                       |

(SRAM) cell. Electrical characteristic, short channel effect, and transfer property are assessed considering different silicon fin thickness and angle employed a calibrated 3D device-circuit coupled simulation technique. To meet the given specification: the subthreshold swing (SS) < 72 mV/dec, the drain induced barrier lowing (DIBL) < 65 mV/V, and static noise margin (SNM) of 6-T SRAM > 85 mV, optimal critical angles of channel fin:  $90^{\circ}$ ,  $80^{\circ}$ , and  $76^{\circ}$  are found for the fin widths: 16, 12, and 8 nm, respectively.

#### Session 2: Solar Cell I (November 20)

#### Room B

Chair: Wei-Sheng Liu, Department of Photonics Engineering, Yuan Ze University, Taiwan

#### 13:30~14:00 (Invited) Semiconductor Nanostructures for Solar Cells

#### (Invited) Semiconductor Nanostructures for Solar

Ching-Fuh Lin, Hong-Jhang Syu, and Thiyagu Subramani

Director of i-PARC and Professor of GIPO, GIEE, & EE Dept., National Taiwan University

Solar energy is one of the good choices to replace conventional fossil energies due to its abundance. However, the limited solar intensity leads to a need of huge areas to harvest sufficient sunlight. Therefore, low cost and high productivity are very important for photovoltaics. Here we report the low-cost approaches to fabricate semiconductor nanostructures for solar cells. First, we use organic materials for light absorption and combine them with ZnO nanorods that are grown using solution process. This platform with ZnO nanorods can lead to PCE of more than 7 % for several organic polymers. The best one is over 8%. Second, Si nanowires are combined with the organic materials to form p-n junction. The fabrication can also be fabricated using low-cost solution processes. The device so far demonstrated PCE near 13 %. We also developed a technique based on chemical etching nano-structures to form very thin single-crystal Si films. The thickness could be from around 5 μm to 20 μm. The rest of the Si wafer can be reused to form more single crystalline Si thin films, so the material cost can be reduced to only 1/10 or less. Details will be discussed.

#### 14:00~14:15

#1134 Fabrication of Deformed  $TiO_2$  Aggregate and Application as Photoanode in Dye Sensitized Solar Cells

Kuo-Che Tseng<sup>1</sup>, Hsueh-Tao Chou<sup>1</sup>, Ho-Chun Hsu<sup>2</sup>

<sup>1</sup>Department of Electronic Engineering, National Yunlin University of Science and Technology, Taiwan <sup>2</sup>Graduate School of Engineering Science and Technology, National Yunlin University of Science and Technology, Taiwan.

The deformed TiO<sub>2</sub> aggregate was synthesized by two-step method with tri-block copolymer as template. The photovoltaic properties of deformed TiO<sub>2</sub> aggregate as photoanode in dye-sensitized solar cells (DSSCs) were investigated. The photoanode of deformed TiO<sub>2</sub> aggregate possesses enhanced light harvesting and a larger amount of dye loading. An overall conversion efficiency of deformed TiO<sub>2</sub> aggregate as photoanode is 2.64% under illumination of simulated AM 1.5G solar light (100 mWcm<sup>-2</sup>). However, the efficiency is lower than the P25 nanoparticles as photoanode (3.1%). The electrochemical impedance spectroscopy (EIS) was performed to investigate electronic processes in DSSCs, and the results showed that deformed TiO<sub>2</sub> aggregate possesses a lot of grain boundaries to hinder the electron transport.

#### 14:15~14:30

### #1213 P-layer Properties on the Performance of a-Si:H p-i-n Solar Cells

Yo-Jin Yang, Yeu-Long Jiang\*, and Yi-Chih Kuo

Graduate Institute of Optoelectronic Engineering and Department of Electrical Engineering, National Chung Hsing University, Taiwan

Various p-layers of hydrogenated amorphous silicon (a-Si:H) p-i-n solar cells were fabricated by plasma-enhanced chemical vapor deposition (PECVD) to investigate the effects of the bandgap (E<sub>g</sub>), the activation energy (E<sub>a</sub>) of p-layer and the double p-layers structure on the performance of solar cells. Increasing the methane gas flow ratio (C<sub>x</sub>) could raise the Eg of p-layer, resulting in the decrease of the light absorption in p-layer, and generating more electron-hole pairs in the i-layer. The open-circuit voltage (Voc) and the short-circuit current density (J<sub>sc</sub>) were increased. However, high bandgap offset at the p/i interface and high energy barrier at the TCO/p interface increased the series resistance (R<sub>s</sub>), and reduced the fill factor (FF). Modulation the methane and diborane gas flow ratio  $(C_x(B_y))$  to obtain the p- layers with the same  $E_g$  but change their  $E_a$ , the results showed that low Ea reduced the Rs, resulting in the increase of FF. Adding a low-E<sub>g</sub> (P<sub>L</sub>) p-layer between the TCO and a high- $E_{\rm g}$  (P<sub>H</sub>) p-layer to form a double p-layers could increase the

conductivity and reduce  $R_s$ , resulting in increase of FF and the efficiency ( $\eta$ ) of a- Si:H p-i-n solar cells.

#### 14:30~14:45

### #1310 Medium Bandgap Conjugated Polymer Merging a Fluorinated Quinoxaline Moiety for Efficient and Air-Stable Solar Cells

Wei-Hsuan Tseng<sup>1</sup>, Jung-Hung Chang<sup>1</sup>, Yun-Chen Chien<sup>2</sup>, Chih-I Wu<sup>1</sup>\*

<sup>1</sup>Department of Electrical Engineering and Graduate Institute of Electrooptical Engineering, National Taiwan University, Taiwan, <sup>2</sup>Department of Chemistry, National Taiwan University, Taiwan.

A new medium-bandgap conjugated copolymer comprising a rigidly fused benzo[1,2-b:4,5-b']- dithiophene (BDT) unit and a fluorinated quinoxaline moiety through a thiophene  $\pi$ -spacer has been rationally designed and synthesized by Stille coupling polymerization and thoroughly evaluated for use as a donor material in bulk- heterojunction polymer solar cells (BHJ PSCs). A comprehensive study of the structure-function relationship in the PSCs was also explored. The PDBTQEH copolymer exhibits good solubility in a wide range of organic solvents and has a high hole mobility. Introduction of highly electronegative fluorine atoms to quinoxaline moiety further lowers both the highest occupied molecular orbital (HOMO) and the lowest unoccupied molecular orbital (LUMO) energy levels of polymer, which is beneficial for attaining higher open-circuit voltage (V<sub>oc</sub>) and long-term stability. The inverted device demonstrates outstanding air stability; without any capsulation, the solar efficiency of the device remains above 74% of the original value after storage in air for 1000 h.

#### 14:45~15:00

### #1363 Development of High-Efficiency Co-Evaporated CIGS Photovoltaic Devices

Chia-Hua Huang\*, Chun-Ping Lin, and Yueh-Lin Jan

Department of Electrical Engineering, National Dong Hwa University, Taiwan

The Cu(In,Ga)Se<sub>2</sub> (CIGS) films were prepared by using a thermal evaporation system equipped with four Knudsen-type effusion cells and an electron impact emission spectroscopy (EIES) system. The evaporation process of the single-stage process with the optimized element flux rates and deposition temperatures as well as the three-stage process were employed for the deposition of CIGS films. Both the element flux rates and the deposition temperatures had critical impacts on the characteristics of CIGS films. Furthermore,

the deposition parameters of the three-stage process were fine tuned for improvement of junction quality and carrier collection of CIGS photovoltaic devices. The properties of the as-prepared CIGS films were investigated. The conversion efficiency of over 17% has been achieved for the fabricated CIGS photovoltaic devices.

#### Session 3: Compound Semiconductor I (November 20)

#### Room C

Chair: Prof. Meng-Chyi Wu, Department of Electrical Engineering & Institute of Electronic Engineering, National Tsing Hua University, Taiwan

## 13:30~14:00 (Invited) Opto/electromechanical resonators based on GaAs/AlGaAs heterostructures

<u>Hiroshi Yamaguchi</u>, Daiki Hatanaka, Imran Mahboob, and Hajime Okamoto NTT Basic Research Laboratories, NTT Corporation, Japan

We will review our recent activities on GaAs/AlGaAs opto/electromechanical resonators. Carrier- mediated optomechanical experiments, including mechanical spectroscopy and thermo-mechanical amplification are presented. We also describe on-chip nonlinear phononic experiments. As the examples, phonon lasing operation and phonon propagation switching are both demonstrated.

#### 14:00~14:15

### #1178 Effect of focused ion beam imaging on the crystallinity of InAs

Tien-Hao Huang<sup>1</sup>, Wei-Chieh Chen<sup>1</sup>, Kuan-Chao Chen<sup>2</sup>, and Hao-Hsiung Lin<sup>1, 2,</sup>

<sub>3\*</sub>

<sup>1</sup>Graduate Institute of Photonics Optoelectronics, National Taiwan University, Taiwan, <sup>2</sup>Graduate Institute of Electronics Engineering, National Taiwan University, Taiwan, <sup>3</sup>Department of Electrical Engineering and Graduate Institute of Electronics Engineering, National Taiwan University, Taiwan

A board band between 220 and 240 cm<sup>-1</sup>, induced by Ga<sup>+</sup> focused ion beam imaging process, has been observed in Raman spectra of InAs. We used spatial correlation model to fit the spectra. The fitting gives a correlation length of ~30Å, implying a severe damage in the surface of InAs.

#### 14:15~14:30

## #1197 Large-Grain Ge-on-Insulator Structure by Rapid-Melting Growth of a-GeSn

Y. Kai<sup>1</sup>\*, R. Matsumura<sup>1,2</sup>, H. Chikita<sup>1</sup>, T. Sadoh<sup>1</sup>, and M. Miyao<sup>1</sup>

<sup>1</sup>Department of Electronics, Kyushu University, Japan, <sup>2</sup>JSPS Reserch Fellow,

Kojimachi, Japan

To realize next generation thin-film-transistors, seedless rapid-melting growth of Ge on insulator is investigated. By rapid-thermal annealing of amorphous GeSn layers on insulating substrates at a temperature between the solidification point and the melting point, GeSn layers melt partially, which generates some solid nuclei as residue. Once cooling starts, liquid-phase epitaxial growth occurs from these nuclei, which results in growth of large-grain crystals. Since segregation coefficient of Sn in Ge is very small (~0.02), almost all Sn atoms segregate at edges of the grown regions. As a result, large-grain pure Ge crystals are achieved on insulating substrates.

#### 14:30~14:45

## **#1243 Demonstrating High-Performance a-InGaZnO Inverter at Room temperature for BEOL Applications**

Li-Jen Chi\*, Yu-Hong Chang, and Tuo-Hung Hou

Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Taiwan

We have successfully fabricated a low-voltage, full-swing enhancement mode-load inverter with a voltage gain close to the ideal value using a-IGZO TFTs fabricated at room temperature. Furthermore, we have also successfully fabricated a low-voltage, full-swing depletion mode-load inverter with a voltage gain up to 40 by demonstrating a depletion-mode a-IGZO TFT fabricated at room temperature. Because of the room-temperature process, they can be easily integrated into the logic BEOL process for SOC to maximize circuit density and functionality.

#### 14:45~15:00

## $\#1345\ NbO_x$ -LAPS and TER for MDCK-E cell culture monitoring

Chen-Ting Yeh<sup>1</sup>, Chia-Ming Yang<sup>1,2,3,4</sup>\*, Shun-Fu Tseng<sup>5</sup>, Tsung-Ru Wu<sup>5</sup>, Hsin-Chih Lai<sup>5</sup>, Chao-Sung Lai<sup>2,3,4</sup>, Wei-Chun Chin<sup>6</sup>, Chih-Hong Lo<sup>7</sup>, Tsann-Long Hwang<sup>7</sup>

<sup>1</sup>Department of Electronic Engineering, Chang Gung University, Taiwan <sup>2</sup>Institute of Electro-Optical Engineering, Chang Gung University, Taiwan <sup>3</sup>Center for Biomedical Engineering, Chang Gung University, Taiwan <sup>4</sup>Healthy Aging Research Center, Chang Gung University, Taiwan <sup>5</sup>Department of Medical Biotechnology and Laboratory Science, Chang Gung University, Taiwan <sup>6</sup>school of Engineering, University of California, Merced, US <sup>7</sup>Department of General Surgery, Chang Gung Memorial Hospital at Linkou

Cell culture progress based on LAPS is presented. A high-dielectric constant material, niobium oxide, was used as the sensing membrane in LAPS. A PDMS well was encapsulated on  $NbO_x$  surface to culture MDCK-E cells. Results of TER and LAPS measurements both support for the cell culture progress by days, which could be used in drug and toxicity effect testing in the future.

| α · 1             | <b>a</b> : ., | o a.   | 1       | NT 1     | 20)    |

|-------------------|---------------|--------|---------|----------|--------|

| <b>5</b> ession 4 | : Circuit     | & Simu | iauon ( | November | ` Z()) |

#### Room D

Chair: Prof. Chen-Hsin Lien, Department of Electrical Engineering & Institute of Electronic Engineering, National Tsing Hua University, Taiwan

## 13:30~14:00 (Invited) High holding voltage SCR devices design for high voltage ESD protection

Zhiwei Liu<sup>1</sup>, Juin J. Liou<sup>2</sup>, Jizhi Liu<sup>1</sup> and Ze Jia<sup>1</sup>

<sup>1</sup>School of Microelectronics and Solid-State Electronics, University of Electronics Science and Technology of China, China <sup>2</sup>School of EECS, University of Central Florida, USA

Electrostatic discharge (ESD) protection for high voltage integrated circuit is challenging due to the requirements of high holding voltage to minimize the risk of ESD-induced latchup and electrical overstress. A high holding voltage can be realized by reducing the emitter injection efficiency of the parasitic BJTs in a SCR device, and it can be accomplished by using a segmented emitter topology. Several type SCR devices with different segmentation pattern and ratio are developed. Experimental data show that the new SCR can posses a holding voltage that is larger than 40V.

#### 14:00~14:15

## #1083 Dual-Directional Silicon-Controlled Rectifier Device for ESD Protection in Biomedical Integrated Circuits

Chun-Yu Lin<sup>1,2</sup> and Yan-Lian Chiu<sup>1</sup>

<sup>1</sup>Department of Electrical Engineering, National Taiwan Normal University, Taiwan <sup>2</sup>Biomedical Electronics Translational Research Center, National Chiao Tung University, Taiwan

To protect the biomedical integrated circuits in CMOS process from electrostatic discharge (ESD) damage, a novel ESD protection device was proposed in this work.

#### 14:15~14:30

## **#1154 Low Voltage and Low Power VCO with Dual-Body-Bias Technique**

Meng-Ting Hsu<sup>1</sup>, An-Cheng Ou<sup>2</sup>, Ruei-wun Jhong<sup>3</sup>

Microwave Communication and Radio Frequency Integrated Circuit Lab, Department and Institute of Electronic Engineering, National Yunlin University of Science and Technology, Taiwan

This paper presents a low voltage, low power voltage-controlled oscillator (VCO) with dual-body-bias technique. The VCO exhibits a measured tuning range of 13.9%. Operating at a low supply voltage of 0.45 V, the core circuit of proposed VCO consumes a low total dc power of 1.04 mW. In this bias condition, the measured average value of phase noise for all frequency ranges is -107.5 dBc/Hz at 1 MHz offset from the carriers.

#### 14:30~14:45

## **#1343** The Influence of the Bonding Wire for the Die-Attach Plate on the CDM ESD Robustness of the Packaged IC Chip

Tzu-Cheng Kao<sup>1,3</sup>, Jian-Hsing Lee<sup>2</sup>, Chen-Hsin Lien<sup>1</sup>, Kuang-Cheng Tai<sup>3</sup> and Hung-Der Su<sup>3</sup>

<sup>1</sup>Institute of Electronics Engineering, National Tsing Hua University, Taiwan <sup>2</sup>GlobalFoundries Inc., USA <sup>3</sup>Richtek Technology Corporation, Taiwan

From the experimental measurements, the largest capacitance for a packaged IC chip comes from the capacitor  $C_{SUB}$ , which exists between the die-attach plate and the metal bus line. It is also found that adding a bonding wire between the die-attach plate and the Vss pin to form a parallel LC resonance circuit can significantly improve the CDM ESD robustness of the packaged IC chip.

#### 14:45~15:00

## #1350 Charging Effect on Gate-Protected Transistors - A Simulation Study

Wallace Lin

National Chiao-Tung University, Taiwan

A simulation study was performed on PMOS transistor charging effect when gate of the transistor is protected. The study concludes that diode protection at transistor gate may not always work as expected. Extra care may be required when one exercises such protection practice in the design of circuits or test structures.

|                                                | Session 5: Novel Device I (November 20)                                         |  |  |  |  |

|------------------------------------------------|---------------------------------------------------------------------------------|--|--|--|--|

|                                                | Room E                                                                          |  |  |  |  |

| Chair: Prof. H                                 | Chair: Prof. Huang-Chung Cheng, Department of Electronics Engineering, National |  |  |  |  |

|                                                | Chiao- Tung University, Taiwan                                                  |  |  |  |  |

| 13:30~14:00                                    | (Invited) Developing a Post-Moore Collaborative Technology                      |  |  |  |  |

| <b>Platform for Emerging Device Deployment</b> |                                                                                 |  |  |  |  |

Lining Zhang\* and Mansun Chan

Department of Electronic and Computer Engineering, The Hong Kong University of Science and Technology, Hong Kong

Due to the emergence of a larger number of new devices with different structure, material and operation mechanisms, evaluation and comparison between them become difficult. To address the need to evaluate the performance of many non-conventional devices in practical applications, a collaborative platform to bridge technology to applications has been developed to create a new eco-system for evaluating new device technologies and accelerating their deployment. The function of the platform as well as the pathway to shorten technology transfer from individual devices to practical circuit in the post-Moore era will be discussed.

#### 14:00~14:15

## #1147 Size Tunable Strain for Germanium Quantum Dots Embedded within SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub>

P. H. Liao<sup>1</sup>, T. C. Hsu<sup>1</sup>, K. H. Chen<sup>1</sup>, T. H. Cheng<sup>2</sup>, T. M. Hsu<sup>2</sup>, and P. W. Li<sup>1</sup>

<sup>1</sup>Department of Electrical Engineering, National Central University, Taiwan <sup>2</sup>Department of Physics, National Central University, Taiwan

Spherical Ge quantum dots (QDs) of desire sizes and locations within the Si-containing layers has been demonstrated using thermal oxidation of SiGe nanopillars over buffer layer of Si<sub>3</sub>N<sub>4</sub> and SiO<sub>2</sub> on the Si substrate. Very large (as much as 4%), size-dependent compressive and tensile strain are observed for the QD embedded in Si<sub>3</sub>N<sub>4</sub> and SiO<sub>2</sub>, respectively. Furthermore, the compressive strain on the Ge QD are confirmed by high resolution transmission electron microscopy (HR-TEM) and Fast-Fourier transforming (FFT). Finally decrease in temperature makes the peak energy, asymmetry, and Gruneisen parameter all appear to have an inverse dependence on the QD size, suggesting that compressive strain, anharmonic effect, and elastic modulus of Ge QDs are enhanced for small QDs.

#### 14:15~14:30

### #1274 Gate Leakage Current Suppression and Reliability Improvement for Ultra-Low EOT Ge MOS Devices by Suitable HfAlO/HfON Thickness Stack and Sintering Temperature

Yan-Lin Li, Kuei-Shu Chang-Liao, Shih-Han Yi, Chen-Chien Li, Wei-Fong Chi, and Li-Jung Liu

Department of Engineering and System Science, National Tsing Hua University,

Ultra-low effective oxide thickness (EOT) Ge MOS devices with

different HfAlO/HfON stacks and sintering temperatures are investigated in this work. The suppression of gate leakage current and improvement of reliability properties can be achieved by either stacked gate dielectrics or a low sintering temperature. Especially, the qualities of interface and high-k gate dielectric for Ge devices are significantly improved through a low sintering temperature. A 0.5 nm HfAlO/ 2.5 nm HfON gate stack and a sintering temperature at 350°C are the suitable conditions to achieve low EOT, gate leakage, and good reliability for Ge MOS devices.

#### 14:30~14:45

## #1316 Ammonia sensing characterization on monolayer graphene/Au electrode by thickness and spacing effect

Tsung-Cheng Chen<sup>1</sup>, Lin Wei-Tse<sup>1</sup>, Hui-Ling Liu<sup>1</sup>, Ming-che Hsiao<sup>1</sup>, Kuan-I Ho<sup>1</sup>, Meng-Chin Su<sup>1</sup>, Ming-Yang Shih<sup>1</sup>, Chia-Ming Yang<sup>1,2,3,4</sup>\* and Chao-Sung Lai<sup>1,3,4</sup>\*

<sup>1</sup>Department of Electronic Engineering, Chang Gung University, Taiwan <sup>2</sup>Institute of Electro-Optical Engineering, Chang Gung University, Taiwan <sup>3</sup>Healthy Aging Research Center, Chang Gung University, Taiwan <sup>4</sup>Center for Biomedical Engineering, Chang Gung University, Taiwan

Ammonia gas sensor was fabrication by monolayer CVD graphene transferred to the interdigitated Au electrode. Electrode spacing and thickness was modified to get a higher response for different ammonia concentration at room temperature. The best ammonia gas sensing performance in this study is Au electrode with thickness and spacing of 120nm and 200um, respectively Ammonia sensing performance improvements could be explained by the bending of graphene and following more binding sites, which could be supported by the Raman mapping results.

#### 14:45~15:00

## #1342 Effects of Illumination on Interface Properties of Al/SiO $_2$ /n-SiC MOS Structure

Po-Kai Chang and Jenn-Gwo Hwu

Graduate Institute of Electronics Engineering, National Taiwan University, Taiwan

Electron injection from the gate is the main component of gate current at negative bias concerning the Al/SiO<sub>2</sub>/n-SiC structure. While the n-type 4H-SiC MOS capacitor is illuminated by tungsten lamp, deep acceptor-like interface states may capture electrons from the valence band, which can block the gate-injected electrons from tunneling through the interface states and give rise to the decrease of gate current. On the contrary, the gate current at negative bias

increases under UV irradiation, however. Then the current drops off even less than the value of dark condition after the UV light is switched off, and gets back to the previous current level by degrees. This represents that trapping of electrons at the interface ought to cause the reduction of gate current at negative bias.

#### Session 6: TFT I (November 20)

#### Room A

Chair: Prof. Steve S. Chung, Department of Electronics Engineering, National Chiao Tung University, Taiwan

#### 15:30~16:00

## (Invited) Suppress Dynamic Hot Carrier Degradation in Four-terminal Poly-Si Thin Film Transistors

Mingxiang Wang\*, Huaisheng Wang, Dongli Zhang

Department of Microelectronics, Soochow Univ., China

Poly-Si TFTs in operation are commonly subjected to the dynamic hot carrier (HC) effect which causes severe device degradation. To suppress dynamic HC induced degradation, four-terminal TFT structure with an added substrate electrode as a carrier injector was proposed. During the pulse transition, carriers will be injected into the channel and diffuse further to the channel-to-source/drain junction. The non-equilibrium state in the depletion region of the junction is suppressed, reducing the dynamic HC effect. The suppression of the degradation is more effective for higher carrier injection level and shorter carrier transport distance.

#### 16:00~16:15

## #1129 Fabrication of Sub-100nm N-Type Junctionless Thin-Film Transistors with a Poly-Si Nanowire Channel

Liang-Hsu Chien<sup>1</sup>, Chin-I Kuan<sup>1</sup>, Ting-Ting Wen<sup>2</sup>, Horng-Chih Lin<sup>1,2,3</sup>, and Tiao-Yuan Huang<sup>1</sup>

<sup>1</sup>Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University <sup>2</sup>Nano Facility Center, National Chiao Tung University, Taiwan <sup>3</sup>National Nano Device Labs, Taiwan

In this study, based solely on I line-based lithography, we fabricated and characterized sub-100nm N-Type juctionless thin-film transistors (TFTs) with a phosphorus-doped poly-Si nanowire (NW) channel. By utilizing the sidewall spacer etching and PR trimming techniques, junctionless poly-Si devices with channel length down to 91 nm and width to 28 nm have been fabricated. Well-behaved device characteristics demonstrate the

|             | fassibility of this mathod for the goodamic studies on none scale                                                           |

|-------------|-----------------------------------------------------------------------------------------------------------------------------|

|             | feasibility of this method for the academic studies on nano-scale devices.                                                  |

| 16 15 16 20 |                                                                                                                             |

| 16:15~16:30 | #1156 The Time Response for the Amorphous In-Ga-Zn-O Thin                                                                   |

|             | Film Transistor under Multiple-Pulsed Illumination Stress                                                                   |

|             | Chun-Yi Chang <sup>1</sup> , and Ya-Hsiang Tai <sup>2</sup>                                                                 |

|             | <sup>1</sup> Department of Photonics & Institute of Electro-Optical Engineering, National                                   |

|             | Chiao Tung University, Taiwan <sup>2</sup> Department of Photonics & Institute of Display,                                  |

|             | National Chiao Tung University, Taiwan                                                                                      |

|             | In this paper, we studied the time response to the multiple-pulse                                                           |

|             | illumination and found that it can be fitted by the formula and                                                             |

|             | parameters. Based on the analysis, the time response to the                                                                 |

|             | multiple-pulse illumination can also be depicted by the same                                                                |

|             | formula and parameters as those to the single pulse of light. It                                                            |

|             | reveals the possibility to use the proposed formula in the more                                                             |

|             | complicated illumination cases, which is important in the                                                                   |

|             | development of transparent electronics using a-IGZO TFT.                                                                    |

| 16:30~16:45 | #1185 Bis-Amino-Silane-Plasma-Deposited Organic-Inorganic-                                                                  |

|             | Hybrid Materials as Gate Dielectrics for ZnO Thin-Film                                                                      |

|             | Transistors                                                                                                                 |

|             | Chen-Hsuan Wen, Yun-Shiuan Li, and I-Chun Cheng*                                                                            |

|             | Graduate Institute of Photonics and Optoelectronics, National Taiwan University,                                            |

|             | Taiwan                                                                                                                      |

|             | Material properties of organic-inorganic-hybrid materials                                                                   |

|             | deposited from bis-amino-silane with oxidants using                                                                         |

|             | plasma-enhanced chemical vapor deposition (PECVD) were                                                                      |

|             | investigated. Films are more inorganic-like when deposited at a                                                             |

|             | higher oxidant dilution ratio. The deposited films were then used as                                                        |

|             | the gate dielectrics for ZnO thin-film transistors. The best achieved                                                       |

|             | device exhibits an on-off current ratio of $>10^6$ , threshold voltage of                                                   |

|             |                                                                                                                             |